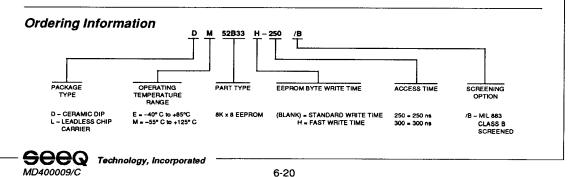

## M52B33/M52B33H E52B33/E52B33H

# 64K Electrically Erasable PROM

October 1989

#### Features

- Full Military and Extended Temperature Range

- M52B33/M52B33H: -55° to 125° C

- E52B33/E52B33H: -- 40° to 85° C

- 10,000 Write Cycles/Byte Over Temperature

- Input Latches

- 5 V ± 10% Vcc

- 1 ms (52B33H) or 9 ms (52B33) TTL Byte Erase/Byte Write

- Power Up/Down Protection

- DiTrace®

- Fast Read Access Time—250 ns

- Infinite Number of Read Cycles

- JEDEC Approved Byte-Wide Memory Pinout

## Description

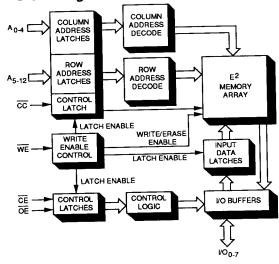

SEEQ's M52B33 and E52B33 are 8192 x 8 bit, 5V electrically erasable programmable read only memories (EEPROMs) which are specified over the military and

#### Block Diagram

DiTrace is a registered trademark of SEEQ Technology Inc.

extended temperature range respectively. They have input latches on all addresses, data, and control (chip and output) lines. In addition, for applications requiring fast byte write time (1 ms), an E52B33H and M52B33H are available. Data is latched and electrically written by a TTL pulse on the Write Enable pin. Once written, there is no limit to the number of times data may be read. The erasure time is under 10 ms, and each byte may be erased and written a minimum of 10,000 times.

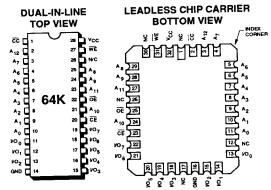

The E/M52B33 is available in a 28 pin cerdip or 32 pad leadless chip carrier. The pin configuration is to the JEDEC approved byte wide memory pinout for these two types of packages. These EEPROMs are ideal for applications that require a non-volatile memory with in-system write and erase capability. Dynamic configuration (the al-

## Pin Configuration

#### Pin Names

| ADDRESSES – COLUMN<br>(LOWER ORDER BITS)           |

|----------------------------------------------------|

| ADDRESSES - ROW                                    |

| CHIP ENABLE                                        |

| OUTPUT ENABLE                                      |

| WRITE ENABLE                                       |

| DATA INPUT (WRITE OR ERASE),<br>DATA OUTPUT (READ) |

| CHIP CLEAR                                         |

| NO CONNECT                                         |

|                                                    |

MD400009/C

SEEQ Technology, Incorporated

6-15

#### M52B33/M52B33H E52B33/E52B33H

teration of opening software in real-time) is made possible by this device. Applications will be found in military avionics systems, programmable character generators, self-calibrating instrument/machines, programmable industrial controllers, and an assortment of other systems. Designing the EEPROMs into eight and sixteen bit microprocessor system is also simplified by utilizing the fast access time zero wait states. The addition of the latches on all data, address and control inputs reduces the overhead on the system controller by eliminating the need for the controller to maintain these signals. This reduces IC count on the board and improves the system performance.

#### Device Operation

SEEQ E/M52B33 and E/M52B33H have six modes of operation (see Table 1) and require only TTL inputs to operate these modes.

To write into a particular location, that byte must first be erased. A memory location is erased by having valid addresses, Chip Enable at a TTL low, Output Enable at TTL high, and TTL highs (logical 1's) presented to all the I/O lines. Write Enable is then brought to a TTL low level to latch all the inputs. The erase operation requires under 10 ms. A write operation is the same as an erase except true data is presented to the I/O lines. The 52B33H performs the same as the E/M52B33 except that the byte erase/byte write time has been enhanced to 1 ms.

A characteristic of all EEPROMs is that the total number of write and erase cycles is not unlimited. The E/M52B33 is designed for applications requiring up to 10,000 write and erase cycles per byte over the temperature range. The write and erase cycling characteristics are completely byte independent. Adjacent bytes are not affected during write/ erase cycling.

After the device is written, data is read by applying a TTL high to WE, enabling the chip, and enabling the outputs.

Data is available, t<sub>CF</sub> time after Chip Enable is applied or t<sub>AA</sub> time from the addresses. System power may be reduced by placing the device into a standby mode. Raising Chip Enable to a TTL high will reduce the power consumption by over 60%.

#### DiTrace

SEEQ's family of EEPROMs incorporate a DiTrace field. The DiTrace feature is a method for storing production flow information in an extra row of EEPROM cells. As each major manufacturing operation is performed the DiTrace field is automatically updated to reflect the results of that step. These features establish manufacturing operation traceability of the packaged device back to the wafer level. Contact SEEQ for additional information on these features.

#### Chip Clear

Certain applications may require all bytes to be erased simultaneously. See A.C. Operating Characteristics for TTL chip erase timing specifications.

## Power Up/Down Considerations

SEEQ's "52B" E2 family has internal circuitry to minimize false erase or write during system V<sub>cc</sub>power up or down. This circuitry prevents writing or erasing under any one of the following conditions:

- V<sub>CC</sub> is less than 3 V.<sup>(1)</sup>

A negative Write Enable transition has not occurred when V<sub>cc</sub> is between 3 V and 5 V.

Writing will also be prevented if CE or OE are in a logical state other than that specified for a byte write in the Mode Selection table.

#### Mode Selection (Table 1)

| Mode                | Function<br>(Pin) | CE<br>(20)      | (1)             | ŌE<br>(22)      | WE<br>(27)      | I/O<br>(11-13,15-19)               |

|---------------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------------------------|

| Read                |                   | V <sub>IL</sub> | V <sub>IH</sub> | V,,             | V <sub>IH</sub> | D <sub>out</sub>                   |

| Standby             |                   | V <sub>IH</sub> | Don't Care      | Don't Care      | Don't Care      | High Z                             |

| Byte Erase          |                   | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IH</sub> | V               | D <sub>IN</sub> = V <sub>IH</sub>  |

| Byte Write          |                   | V,,             | V <sub>IH</sub> | V <sub>IH</sub> | V               | D <sub>in</sub>                    |

| Chip Clear          |                   | V <sub>IL</sub> |                 | V <sub>iH</sub> | V               | V <sub>IL</sub> or V <sub>IH</sub> |

| Write/Erase Inhibit |                   | V <sub>IH</sub> | Don't Care      | Don't Care      | Don't Care      | High Z                             |

#### NOTE:

Characterized. Not tested.

**500** Technology, Incorporated

#### M52B33/M52B33H E52B33/E52B33H

#### Absolute Maximum Stress Ratings\*

| Temperature                     |                        |

|---------------------------------|------------------------|

| Storage                         | 65°C to +150°C         |

| Under Bias                      | 65°C to +135°C         |

| D.C. Voltage applied to all Inp | uts or Outputs         |

| with respect to ground          | +6.0 V to -0.5 V       |

| Undershoot/Overshoot pulse of   | of less then 10 ns     |

| (measured at 50% point) appli   | lied to all inputs or  |

| outputs with respect to grou    | nd (undershoot) -1.0 V |

| , ,                             | (overshoot) + 7.0 V    |

\*COMMENT: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### Recommended Operating Conditions

| V <sub>cc</sub> Supply Voltage              | 5 V ± 10%        |

|---------------------------------------------|------------------|

| Temperature Range:<br>M52B33/M52B33H (Case) | -55°C to +125°C  |

| E52B33/E52B33H (Ambient)                    | -40° C to +85° C |

#### **Endurance and Data Retention**

| Symbol          | Parameter         | Value  | Units       | Condition                       |

|-----------------|-------------------|--------|-------------|---------------------------------|

| N               | Minimum Endurance | 10,000 | Cycles/Byte | MIL-STD 883 Test<br>Method 1033 |

| T <sub>on</sub> | Data Retention    | >10    | Years       | MIL-STD 883 Test<br>Method 1008 |

### D.C. Operating Characteristics During Read or Erase/Write

(Over the operating V<sub>cc</sub> and temperature range)

| Symbol           | Parameter                                     | Min. | Nom. | Max.                | Unit                     | Test Conditions                           |

|------------------|-----------------------------------------------|------|------|---------------------|--------------------------|-------------------------------------------|

| I <sub>IN</sub>  | Input Leakage Current                         |      |      | 10                  | μА                       | V <sub>IN</sub> = V <sub>CC</sub> Max.    |

| 10               | Output Leakage Current                        |      |      | 10                  | μА                       | V <sub>out</sub> = V <sub>cc</sub> Max.   |

| I <sub>we</sub>  | Write Enable Leakage<br>Read Mode<br>W/E Mode |      |      | 10<br>10            | μ <b>Α</b><br>μ <b>Α</b> | WE = V <sub>IH</sub> WE = V <sub>IL</sub> |

| I <sub>cc1</sub> | V <sub>cc</sub> Standby Current               |      | 15   | 50                  | mA                       | CE = V <sub>IH</sub>                      |

| I <sub>cc2</sub> | V <sub>cc</sub> Active Current                |      | 50   | 120                 | mA                       | CE = OE = V <sub>IL</sub>                 |

| V <sub>IL</sub>  | Input Low Voltage                             | -0.1 |      | 0.8                 | ٧                        |                                           |

| V <sub>iH</sub>  | Input High Voltage                            | 2    |      | V <sub>cc</sub> + 1 | ٧                        |                                           |

| V <sub>oL</sub>  | Output Low Voltage                            |      |      | 0.45                | ٧                        | I <sub>OL</sub> = 2.1 mA                  |

| V <sub>oh</sub>  | Output High Voltage                           | 2.4  |      |                     | V                        | I <sub>OH</sub> = -400 μA                 |

NOTE: See next page for notes.

**SEEQ** Technology, Incorporated

6-17

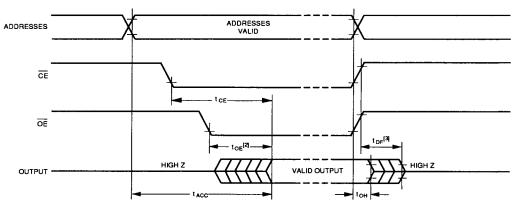

#### A.C. Operating Characteristics During Read (Over the operating Voc and temperature range)

|                                           |                                 | Device              |      | 2B33       |      | 2B33         |          |                                                                                                     |

|-------------------------------------------|---------------------------------|---------------------|------|------------|------|--------------|----------|-----------------------------------------------------------------------------------------------------|

| Symbol                                    | Parameter                       | Number<br>Extension | Min. | Max.       | Min. | B33H<br>Max. | Units    | Test Conditions                                                                                     |

| t <sub>AA</sub>                           | Address Access Time             | -250<br>-300        |      | 250<br>300 |      | 250<br>300   | ns<br>ns | CE = OE ≠V <sub>IL</sub>                                                                            |

| t <sub>CE</sub>                           | Chip Enable to Data Valid       | -250<br>-300        |      | 250<br>300 |      | 250<br>300   | ns<br>ns | OE = V <sub>IL</sub>                                                                                |

| t <sub>oe</sub> [2]                       | Output Enable to Data Valid     | -250<br>-300        |      | 90<br>90   |      | 90<br>90     | ns<br>ns | CE = V <sub>IL</sub>                                                                                |

| t <sub>DF</sub> <sup>[3]</sup>            | Output Enable to High Impedance | -250<br>-300        | 0    | 70<br>70   | 0    | 70<br>70     | ns<br>ns | CE = V <sub>IL</sub>                                                                                |

| t <sub>oH</sub>                           | Output Hold                     | All                 | 0    |            | 0    |              | ns       | CE = OE = V <sub>IL</sub>                                                                           |

| C <sub>IN</sub> /<br>C <sub>OUT</sub> [4] | Input/Output Capacitance        | All                 |      | 10         |      | 10           | pF       | $V_{IN} = 0 \text{ V for}$ $C_{IN}, V_{OUT} = 0 \text{ V}$ for $C_{OUT}$ $T_A = 25^{\circ}\text{C}$ |

#### Read Cycle Timing

#### NOTES:

- 1. Nominal values are for  $T_A = 25^{\circ}$  C and  $V_{CC} = 5.0$ V.

- 2. OE may be delayed to  $t_{AA} t_{OE}$  after the falling edge of CE without impact on  $t_{AA}$ .

- 3. top is specified from OE or CE, whichever occurs first.

- 4. This parameter is measured only for the initial qualification and after process or design changes which may affect capacitance.

- 5. After t<sub>H</sub>, hold time, from WE, the inputs CE, OE, CC, Address and Data are latched and are "Don't Cares" until t<sub>WR</sub>, Write Recovery Time, after the trailing edge of WE.

- 6. The Write Recovery Time, t<sub>WR</sub>, is the time after the trailing edge of WE that the latches are open and able to accept the next mode set-up conditions. Reference Table 1 (page 2) for mode control conditions.

- 7. These are equivalent test conditions and actual test conditions are dependent on the tester.

Technology, Incorporated

## Equivalent A.C. Test Conditions [7]

Output Load: 1 TTL gate and C<sub>L</sub> = 100 pF Input Rise and Fall Times: ≤ 20ns Input Pulse Levels: 0.45 V to 2.4 V Timing Measurement Reference Level: Inputs 1 V and 2 V Outputs 0.8 V and 2 V

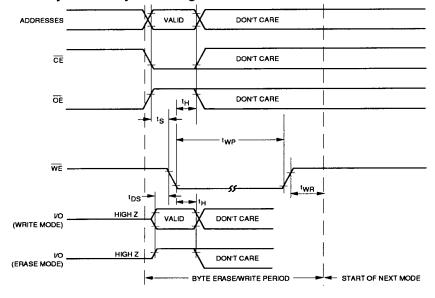

#### A.C. Operating Characteristics During Write/Erase

(Over the operating V<sub>cc</sub> and temperature range)

| Symbol                        | Parameter                                                 | Min. | Max. | Units |

|-------------------------------|-----------------------------------------------------------|------|------|-------|

| i <sub>s</sub>                | CE, OE or Address Setup to WE                             | 50   |      | ns    |

| t <sub>os</sub>               | Data Setup to WE                                          | 15   |      | ns    |

| t <sub>H</sub> <sup>[5]</sup> | WE to CE, OE, Address or Data Change                      | 50   |      | ns    |

| t <sub>wP</sub>               | Write Enable, (WE) Pulse Width Byte Modes — M52B33/E52B33 | 9    |      | ms    |

|                               | Byte Modes — M52B33H                                      | 1    | _    | ms    |

| t <sub>wn<sup>[6]</sup></sub> | WE to Mode Change WE to Next Byte Write/Erase Cycle       | 50   |      | ns    |

|                               | WE to Start of a Read Cycle                               | 1    |      | μs    |

## Byte Erase or Byte Write Cycle Timing

NOTES

See previous page for notes.

**SEQ**MD400009/C

SEEQ Technology, Incorporated

## A.C. Operating Characteristics During Chip Erase.

(Over the operating V<sub>cc</sub> and temperature range)

| Parameter                                                                             | Min.                                                                                                                                                                                            | Max.                                                                                                                                                                                                           | Units                                                                                                                                                                                                          |

|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CC, CE, OE Setup to WE                                                                | 50                                                                                                                                                                                              |                                                                                                                                                                                                                | ns                                                                                                                                                                                                             |

| WE to CE, OE, CC change                                                               | 50                                                                                                                                                                                              |                                                                                                                                                                                                                | ns                                                                                                                                                                                                             |

| Write Enable (WE) Pulse Width Chip Erase —M52B33/M52B33H Chip Erase — E52B33H/E52B33H | 10                                                                                                                                                                                              |                                                                                                                                                                                                                | ms                                                                                                                                                                                                             |

| WE to Mode change WE to Start of Next Byte Write Cycle                                | 50                                                                                                                                                                                              |                                                                                                                                                                                                                | ns                                                                                                                                                                                                             |

| WE to Start of Read Cycle                                                             |                                                                                                                                                                                                 | 1                                                                                                                                                                                                              | μs                                                                                                                                                                                                             |

|                                                                                       | CC, CE, OE Setup to WE  WE to CE, OE, CC change  Write Enable (WE) Pulse Width Chip Erase — M52B33/M52B33H Chip Erase — E52B33H/E52B33H  WE to Mode change WE to Start of Next Byte Write Cycle | CC, CE, OE Setup to WE 50  WE to CE, OE, CC change 50  Write Enable (WE) Pulse Width 10  Chip Erase — M52B33/M52B33H  Chip Erase — E52B33H/E52B33H  WE to Mode change 50  WE to Start of Next Byte Write Cycle | CC, CE, OE Setup to WE 50  WE to CE, OE, CC change 50  Write Enable (WE) Pulse Width 10  Chip Erase — M52B33/M52B33H  Chip Erase — E52B33H/E52B33H  WE to Mode change 50  WE to Start of Next Byte Write Cycle |

### TTL Chip Erase Timing

NOTE: Address, Data are don't care during Chip Clear.